854S712AKILF是 Renesas 推出的时钟缓冲器,主要用于需要时钟信号分配或缓冲的场景。以下是其核心参数:类型:扇出缓冲器(分配)电路数:1比率 - 输入:输出:1:2差分 - 输入:输出:是/是输入:CML,LVDS,LVPECL输出:LVDS频率 - 最大值:3 GHz电压 - 供电:3.135V ~ 3…

854S712AKILF是 Renesas 推出的时钟缓冲器,主要用于需要时钟信号分配或缓冲的场景。以下是其核心参数:

类型:扇出缓冲器(分配)

电路数:1

比率 - 输入:输出:1:2

差分 - 输入:输出:是/是

输入:CML,LVDS,LVPECL

输出:LVDS

频率 - 最大值:3 GHz

电压 - 供电:3.135V ~ 3.465V

工作温度:-40°C ~ 85°C

安装类型:表面贴装型

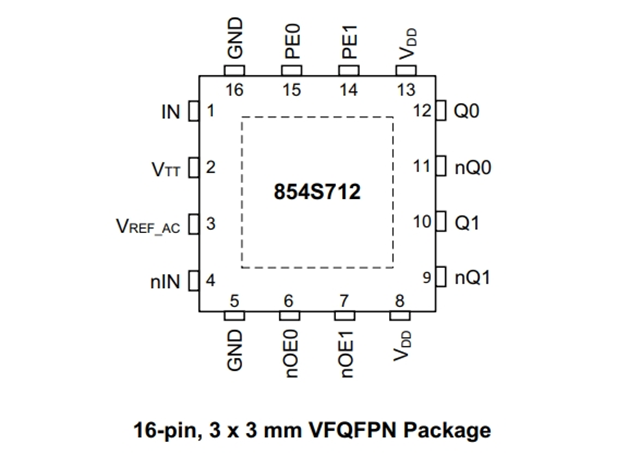

封装/外壳:16-VFQFN

介绍

854S712AKILF是一款差分、高速1:2数据/时钟扇出缓冲器和线路驱动器。输出支持预加重,以便驱动背板和长传输线,同时降低符号间干扰效应。预加重级别可配置为针对低误码率或低功耗进行优化。预加重对转换位使用增加的输出电压摆幅。

854S712AKILF针对高达 4.5Gbps(NRZ)的数据速率、数据应用中的确定性抖动和时钟应用中的低附加抖动进行了优化。854S712AKILF的输出符合 LVDS 标准,而差分输入则兼容各种信号电平,如 LVDS、LVPECL 和 CML。内部输入端接、用于交流耦合和小型封装(VFQFN)的偏置电压输出支持节省空间的电路板设计。854S712AKILF采用 3.3V 电源供电,支持 -40°C 至 85°C 的工业温度范围。

854S712AKILF产品特性

1:2差分数据/时钟扇出缓冲器和线路驱动器

4.5 Gbps 数据速率 (NRZ)(最大值)

差分LVDS输出

支持 LVDS、LVPECL 和 CML 电平的差分输入

可配置的输出预加重

低偏斜输出:10ps(最大)

低数据确定性抖动:4ps(最大)

控制输入的LVCMOS接口电平

异步输出禁用进入高阻抗状态

内部输入端接:100?(差分)

附加相位抖动,RMS:0.08ps(典型值)

全 3.3V 电源电压

-40°C 至 85°C 环境工作温度

采用无铅 (RoHS 6) 封装

应用场景

854S712AKILF适用于需要时钟信号分配或缓冲的场景,例如:

高速数字电路设计

通信设备时钟管理

工业控制系统的时钟同步

该器件通过JESD-30和JESD-609标准认证,符合电子行业对时钟信号完整性的要求。

供货信息

如需采购854S712AKILF时钟缓冲器,欢迎联系明佳达电子(www.hkmjd.com)。

电话咨询:86-755-83294757

企业QQ:1668527835/ 2850151598/ 2850151584/ 2850151585

服务时间:9:00-18:00

联系邮箱:chen13410018555@163.com/sales@hkmjd.com

公司地址:广东省深圳市福田区振中路新亚洲国利大厦1239-1241室

CopyRight©2022 版权归明佳达电子公司所有 粤ICP备05062024号-12

官方二维码

友情链接: